# PLASMA SPARK PROJECT

# PWM pulse generation card GH01 version 1.3

**Translator** : jeromero (Jérome)

# **Previous part**

The integrated circuit U3 (4049) is a CMOS technology.

Thus, you must be really careful to avoid premature damage :

- Upon delivery, the component should be plugged into a plate of polystyrene foam covered with a sheet of aluminum foil (in order to give all the pins the same potential).

- > When handling this component, try to not touch the pins.

For all manipulations of IC (insert or change) described in this document, you must perform this operation power cut. This provision is implicit and will not be remembered. Regularly during the testing procedure, it is necessary to regularly check if components are overheating.

# **Files**

Files required :

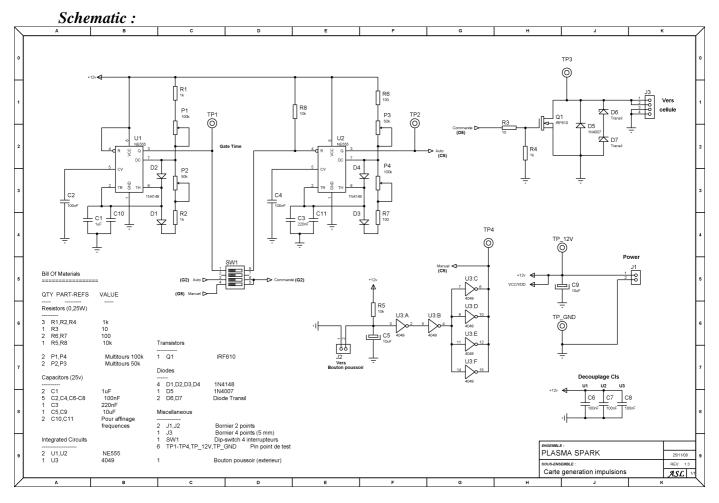

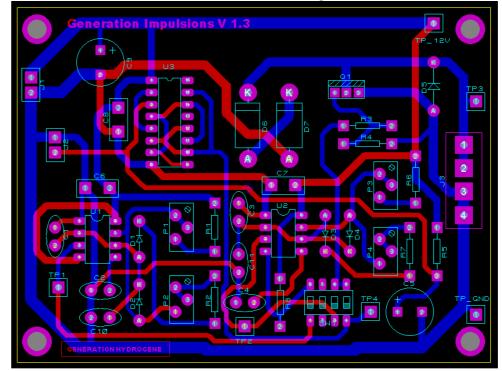

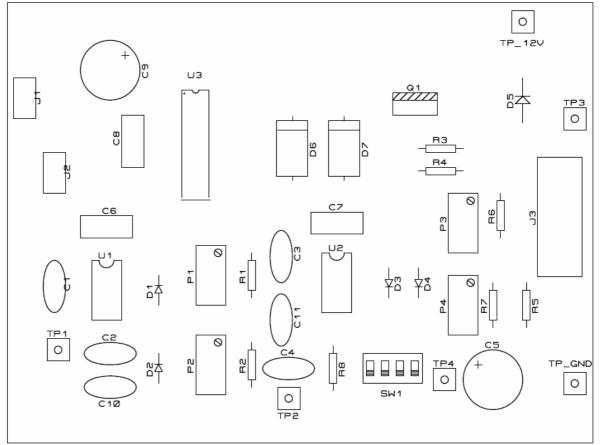

| GH01 v1.3 Schématique.pdf              | Electronic map              |

|----------------------------------------|-----------------------------|

| GH 01 v1.3 Implantation composants.pdf | Component layout on the map |

| GH01 v1.3 Face composants.pdf          | Component side PCB artwork  |

| GH01 v1.3 Face soudure.pdf             | Weld side artwork           |

# **Double-side PCB Realization**

The card is double side.

Size 3" x 3,9".

There are several methods to make a double-sided circuit.

The one retained for our project is Francis's one (nickname "fc89" on the Forum) which provides great ease of realization with reasonable accuracy.

After cleaning and degreasing the tracks, drill the correct diameters.

Four pellets of large size (at the four corners of the PCB) are provided to mount the card on spacers - screw 1 to 1.5 mm and nuts, which allows the card to not touch the work plan.

Don't forget to make regular visual checks in order to avoid omission.

Tinning of all the "power" tracks : 12v line, ground line and power tracks between the mosfet and J3 and also between the mosfet and diodes transil (optional).

Operation necessary to provide a thicker track and therefore better current flow.

# PCB Artwork

*Blue* = weld side, red side = components side

# Welding components

No crossing.

The "way" between the layers is performed, when necessary, by the components pins. In order to avoid omission, we advice you to weld both side of each components pins. Components which need to be welded only on weld side:

> Connector J3 3 trimmers (P1, P2 and P3) C6 et C5 Q1 (mosfet)

#### Components layout :

Welding to be made according to the thickness of the "layer" of the various components (from lowest to highest) :

- 1. 1N4148 diodes

- 2. Resistors

- 3. 1N4007 diode

- 4. Tulip supports

- 5. Small capacitors

- 6. Check points (resistors pins)

- 7. Decoupling capacitors

- 8. Trimmers

- 9. Connector J3

- 10. Electrochemical capacitors

The sequence of the "layers" may be modified depending on the component height.

#### DON'T WELD THE MOSFET Q1, THIS WILL BE DONE AFTER THE FIRST CHECKINGS

For each "layer", first weld the component side, then weld the weld side and systematic visual inspection before proceeding to the next "layer".

Each pin of all components must be welded on both side. This requires the provision of supports type tulip for IC.

#### Finalized PCB :

# **Electrical test**

At this level, no IC is plugged.

Weld the ground wire of your power supply in 2 of J1. Connect the ammeter between the +12 v power supply and 1 of J1. At power up, **POWER MUST BE 0**. If it is not, check welds to avoid potential short-circuit.

Then, it is required to verify the 12v input for each circuit :

In the multimeter, check for 12v between all of the following pins (example: 1-4 = measure between pin 1 and 4):

| <b>U1</b> | 1-4;1-8 |

|-----------|---------|

| <b>U2</b> | 1-4;1-8 |

| <b>U3</b> | 1-8     |

# <u>Plug IC</u>

Do not weld yet the MOSFET Q1.

Put the switch SW1 on its support with all levers directed towards the edge of the PCB and all switched OFF (contacts open).

Connect the ammeter between your power supply +12 v and 1 of J1.

Record the intensity. Consumption must be low (around a few mA). If all right, connect the +12 v power supply to 1 of J1 by a cord.

#### Checking noise on the 12v line

Oscillograph on alternating mode. Range 0.1 V / div or less. Measure (function of ground TP\_GND) noise on each power input of each IC :

|           |          | Valeurs relevées<br>sur la carte |

|-----------|----------|----------------------------------|

| <b>U1</b> | Broche 8 | <b>0</b> v                       |

| U2        | Broche 8 | <b>0</b> v                       |

| U3        | Broche 1 | <b>0</b> v                       |

You must have, for each IC, a peak-peak signal which should not exceed 0.2 V. If it is, you will have to increase the value of C9 or C6 to C8, depending on the IC causing trouble.

# **Time slots checking**

1 / U1 - Oscillograph measure in TP1 (P1 adjusts the time slot on top level state and P2 on low level state).

Set P1 on mini => record the duration of the top slot. P2 on mini => record time slot low level P2 on maxi => record time slot low level

Set P1 on maxi => record the duration of the top slot. P2 on mini => record time slot low level P2 on maxi => record time slot low level

| <b>U1</b>   | Slot hight level | Slot low level |

|-------------|------------------|----------------|

| Avec P1 min | 680µs            |                |

| P2 min      | -                | 680µs          |

| P2 max      | -                | 75ms           |

| Avec P1 max | 163ms            |                |

| P2 min      | -                | 650µs          |

| P2 max      | -                | 72ms           |

2 / Set P1 on the maximum (to get the largest slot).

3 / U2 – Oscillograph measure on TP2 (*P2 adjusts the duration of the slot top level state and P3 the slot low level state*).

SW1 1-8 switch ON (gate time ON - enabling U2).

Set P3 on mini => record the duration of the top slot. P4 min => record time slot low level P4 max => record time slot low level Set P3 on maxi = record the duration of the top slot.

P4 on mini => record time slot low level

| U2          | Slot hight level | Slot low level |

|-------------|------------------|----------------|

| Avec P3 min | 16µs             |                |

| P4 min      | -                | 32µs           |

| P4 max      | -                | 43ms           |

| Avec P3 max | 8ms              |                |

| P4 min      | -                | 20µs           |

| P4 max      | -                | 16,6ms         |

P4 on maxi => record time slot low level

4 / SW1 1-8 switched OFF (No gate time - U2 off).

In TP2 you must get a continuous train (without gate time).

#### Switch ON SW1 1-8.

# Checking the pulse train

5 / Oscillograph measure on TP2. If necessary, adjust P2 and P3 to get short slots.

You must get pulse trains (duration defined by P1) with a gate time between each train (duration defined by P2).

- 6 / SW1 3-6 (Auto) switched OFF. Common point measure of R3/R4. You should get no signal.

- 7 / SW1 3-6 (Auto) switched ON. Common point measure of R3/R4. You must have previously measured pulse trains.

# Checking the manual command

8 / Weld wires of the push button on J2.

SW1 3-6 (Auto) switched OFF and SW1 4-5 (Manual) switched ON. Handling to be performed in SEQUENCE. SW1 3-6 and 4-5 mustn'nt be both switched ON!

Oscillograph on common point of R3/R4.

With proper adjustment of oscillograph timebase, check that each time you press the button there is one 0-12V pulse and, if possible, verify that each time you push there is <u>only one</u> single pulse.

Otherwise, the debounce circuit is too low, increase the value of R5 and C5.

# **Checking output**

9 / After having stopped the power supply, weld the mosfet Q1.

And connect a 10 k $\Omega$  resistor between 1 of J3 and the power supply +12v. Oscillograph on TP3. Power-supply ON.

You must get the pulse train back (inverted) amplitude 12v - 0v.

Subject to mistakes or omissions... On October 2, 2010 **Asl**

Terms of use

This document may be freely redistributed, but always in its entirety.

All rights to the content of this document, text and diagrams that come with, remain the exclusive property of *Génération Hydrogène*.

Thus, any partial copy or reproduction is strictly prohibited.

The author will not be held responsible, under no circumstances, due to any direct or indirect consequence resulting from reading and / or applying the concept described in this document.

Any commercial use is prohibited without the agreement of the *Génération Hydrogène* administrator.